Hdl Design Flow

Xilinx fpga design flow.

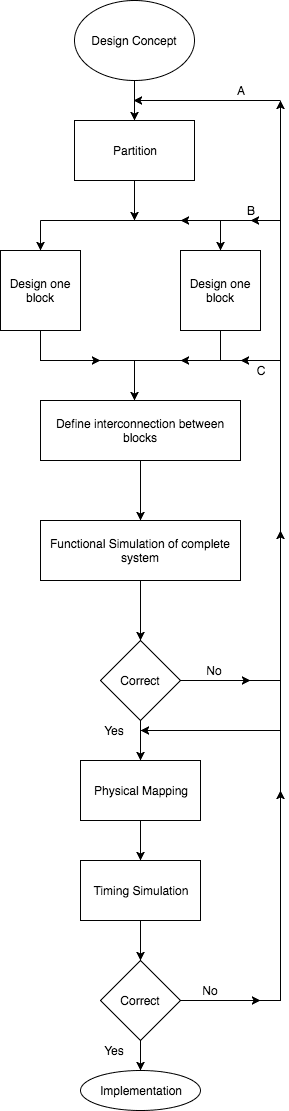

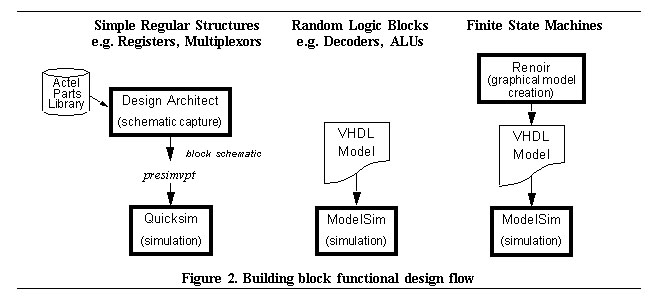

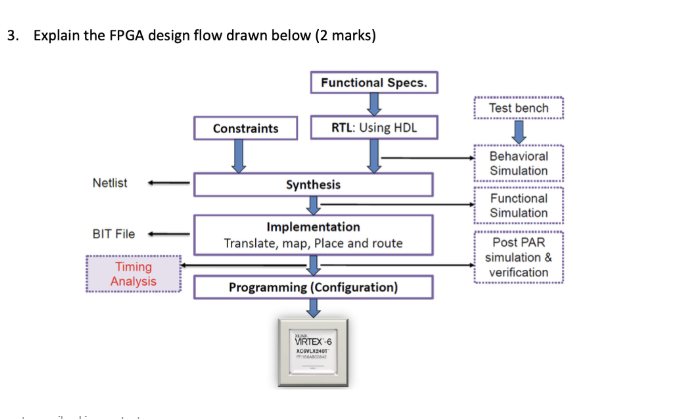

Hdl design flow. If the designer wants to deal more with hardware then schematic entry is the better choice. Schematic based hardware description language and combination of both etc. Through hardware description language or hdl or you may even combine the two and use a best of both worlds approach using tools that can convert hdl into schematics and vice versa depending on your fpga design and preference.

Prabhu goel the inventor of the podem test generation algorithm. Xilinx ise design suite supports all the programmable devices from xilinx including zynq 7000. There are different techniques for design entry.

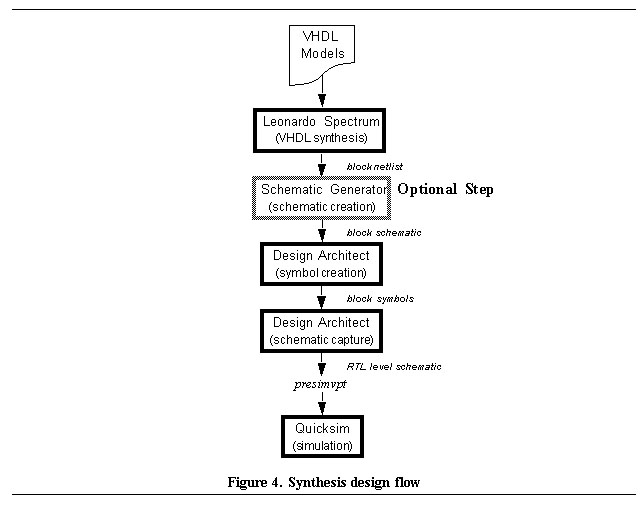

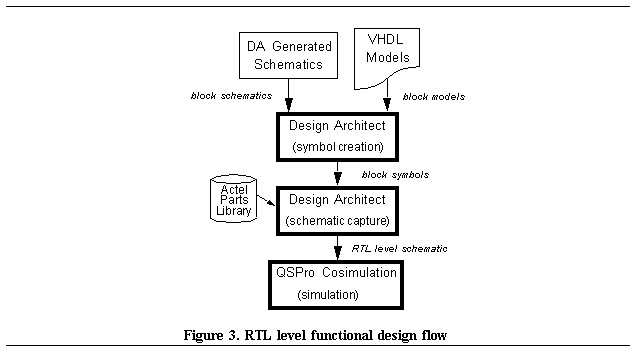

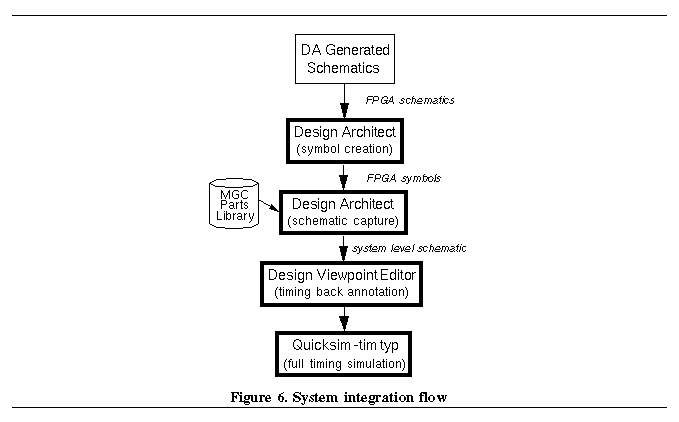

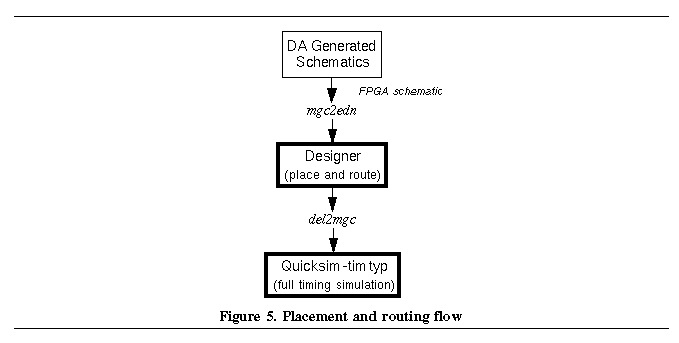

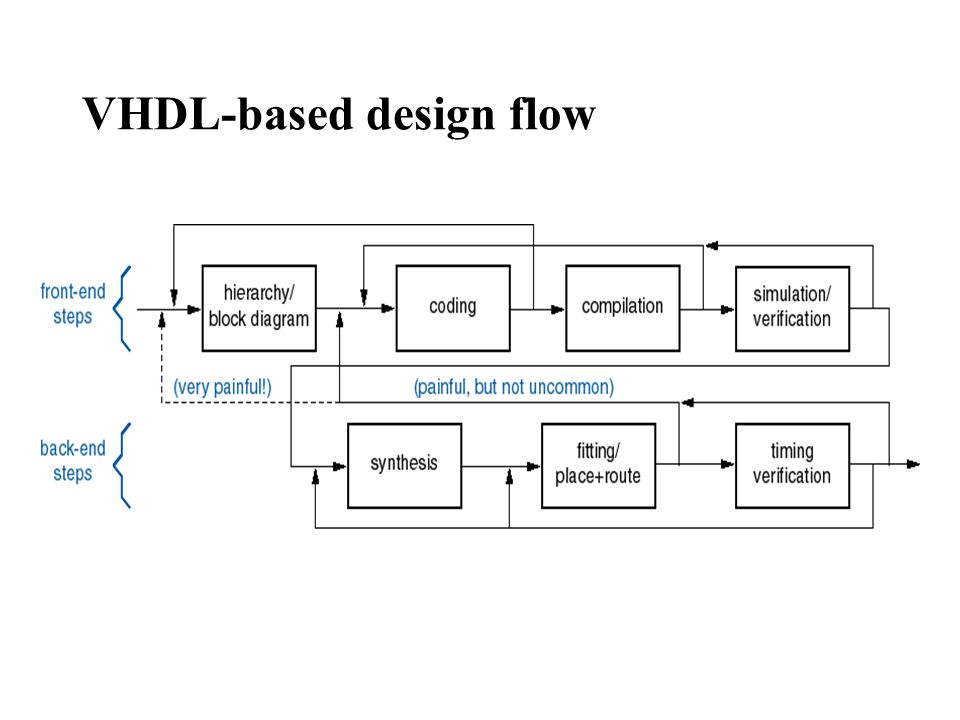

In general as the design flow progresses toward a physically realizable form the design database becomes progressively more laden with technology specific information which cannot be stored in a generic hdl description. The fpga design flow comprises of several different steps or phases including design entry synthesis. Verilog hdl was designed by phil moorby who was later to become the chief designer for verilog xl and the first corporate fellow at cadence design systems.

C to hdl tools and flow have a similar aim but with c or c like programming languages. Selection of a method depends on the design and designer. Silicon vendor supported devices pre compiled simulation libraries ip cores encryption design flow manager integration aldec simulator integration.

Currently xilinx provides two development platforms for fpga and soc users. Xilinx vivado design suite is a next generation development platform for soc strength designs and is more geared towards system level integration and implementation. Ema1997 general design flow i 13 of 24 rtl and behavioral design behavioral synthesis a gap between domain specific tools and rtl synthesis tools a higher level of abstraction for the designer to logic synthesis hdl design flow initial model in c or c or simulation vhdl define and test the functional aspects of the design.

This is specially designed for the pre final and final year engineering students to start learning the vlsi fundamentals while doing their engineering itself. The company was privately held at that time by dr. The use of flow based design tools in engineering is a reasonably new trend.

Verilog hdl originated at automated integrated design systems later renamed as gateway design automation in 1985. The use of flow based design tools allows for more holistic system design and faster development.